A200 产品规格书

Copyright

本文件为知合计算技术(上海)有限公司(以下简称“--公司--”)的财产,未经公司同意或书面同意,不得向任何第三方披露、给予或转让。如违反本条规定,给公司造成损失的,应当承担赔偿责任。

Contacts

知合计算技术(上海)有限公司

地址: 上海市浦东新区申江路 5005 弄星创科技广场 3 号楼 12F

邮箱: business@zhcomputing.com

电话: 0571-87208790

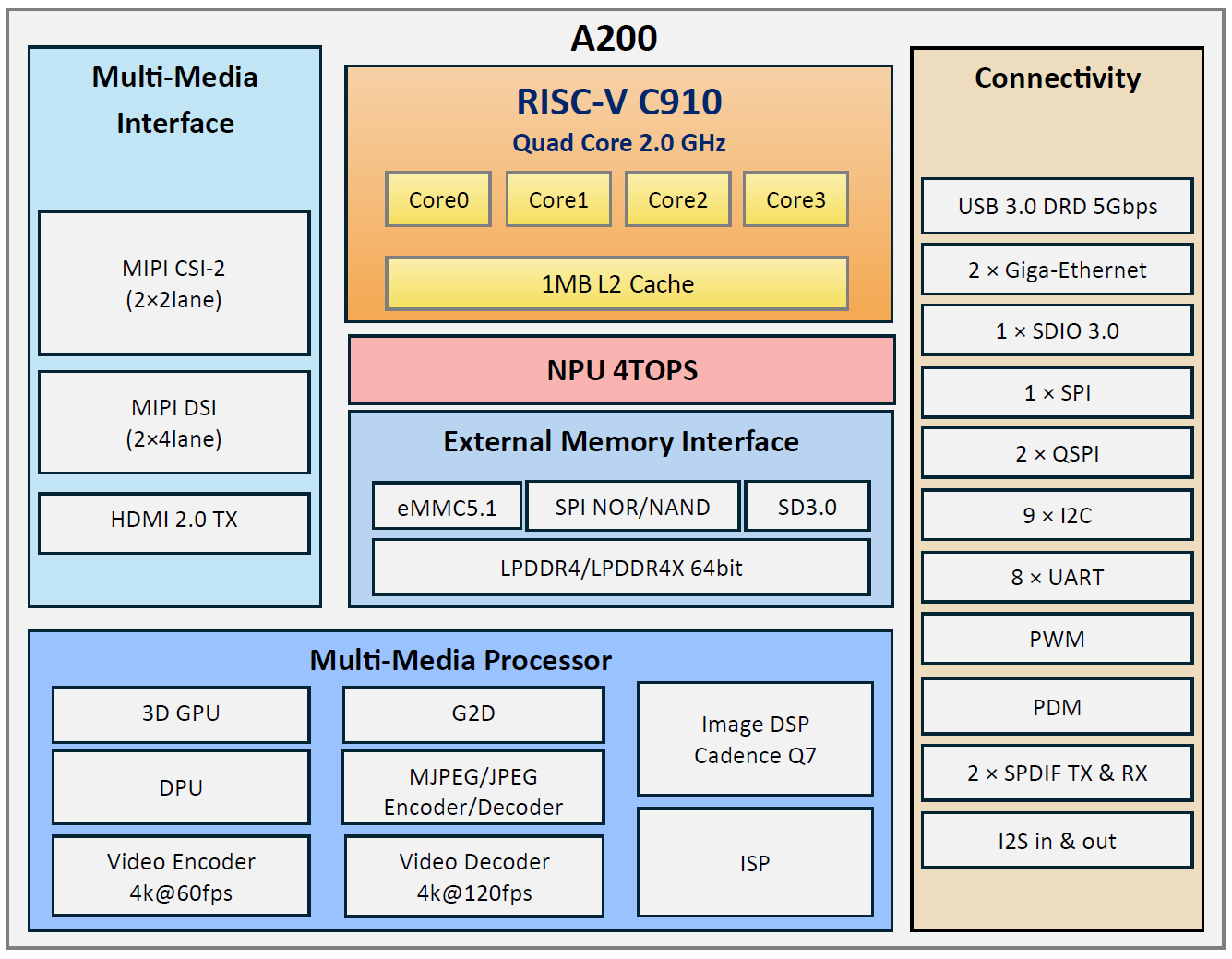

简介

A200 是一款低功耗、高性能、高安全、多模态感知和多媒体 AP 能力的 AI 处理器芯片,可用于刷脸支付终端、AI边缘计算、视频会议一体机、人脸识别考勤门禁、带屏智能音箱等应用场景。基于多核异构架构,集成 RISC-V指令架构的四核 C910 和单核 C906 处理器。

内嵌多个强大硬件加速引擎,提供性能优化的高端应用。支持 H.265/H.264/VP9 标准视频编码,最高分辨率达 4K@60fps,支持H.265/H.264/VP9/AVS2 等多格式视频解码,最高分辨率达 4K@120fps,支持 JPEG 编解码,最高分辨率达 32Kx32K。

内嵌 3D GPU 完全兼容 OpenGL ES3.0/3.1/3.2,OpenCL 1.1/1.2/2.0 和 Vulkan 1.1/1.2,支持 2D 加速引擎,以及通用 DSP 加速器。

支持双通道外部存储器接口,支持 LPDDR4/LPDDR4X ,提供最大存储带宽达 34GB/s,同时提供满足多变应用的外设接口。

功能特性

高性能处理器核

-

四核 RISC-V 64GCV 指令集架构 C910,最高主频可达 2GHz

-

支持小端模式

-

9~12 级深流水架构

-

3 发射 8 执行的超标量架构,对软件完全透明

-

按序取指,乱序发射,乱序完成和按序退休

-

两级高缓结构,哈佛结构一级高缓和共享的二级高缓

-

一级缓存支持 MESI 的一致性协议,二级缓存支持 MOESI 的一致性协议

-

每核支持 64KB I cache 和 64KB D Cache

-

四核共享 1MB L2 Cache

-

支持私有中断控制器 CLINT 和公有中断控制器 PLIC

-

两级 TLB 内存管理单元,实现虚实地址转换与内存管理

-

指令高缓路预测的低功耗访问技术

-

短循环缓存的低功耗执行技术

-

支持 segment load、store 指令

-

支持计时器功能

-

支持 TEE 和 REE,TEE/REE 支持核数启动时可配置

-

支持 Linux 和 Android

-

支持自定义且接口兼容 RISC-V 的多核调试框架

-

独立电源域,支持 DVFS

AI 计算引擎

-

支持 4TOPS@INT8 通用 NNA 算力,主频 1GHz

-

支持 INT8, INT16

-

支持 TensorFlow,ONNX,Caffe

-

支持 CNN,DNN 等

-

支持卷积、激活、单元操作(加法、乘法、最大值、最小值)、池化(最小值、最大值、平均值)、归一化、反卷积

-

无损权重数据压缩

-

灵活比特深度支持:灵活的输入输出和中间数据位深度,8~16 位

-

带宽缩减:

-

支持权重压缩,最小化 DDR 带宽需求,降低功耗

-

支持片上缓存,存储网络中间层数据,减小网络运行对 DDR 带宽需求

-

存储接口

-

片内存储

-

片内 SRAM:128KB

-

片内共享 SRAM:1.5 MB

-

-

片外存储

-

LPDDR4/LPDDR4X

-

支持 32/64 位 LPDDR4/LPDDR4X,最高速率 4266Mbps

-

兼容 JEDEC 标准LPDDR4-2133/LPDDR4-3200/LPDDR4-3733/LPDDR4-4266/LPDDR4X-2133/LPDDR4X-3200/LPDDR4X-3733/LPDDR4X-4266 SDRAM

-

支持 2 个通道,每个通道 32 位数据位宽

-

最大 16GB 地址空间

-

32 位和 64 位软件可配置

-

支持不同 LPDDR4/4X 颗粒时序参数可配置

-

命令重排序和调度,最大化带宽利用率

-

ODT 电阻可编程,动态 PVT 补偿

-

-

SPI NOR/NAND Flash 接口

-

支持 2 路 QSPI,1 路 SPI

-

QSPI0 最高 100MHz,QSPI1 和 SPI 最高 66MHz

-

支持 1 位/2 位/4 位数据线模式传输

-

2 个 QSPI 接口,可配置为 Mode0/Mode1/Mode2/Mode3

-

-

eMMC5.1 接口,最高速率支持 HS400

-

兼容 JEDEC 标准 eMMC5.1 和 eMMC5.0

-

支持 HS400,HS200,DDR52 模式

-

支持 eMMC 启动

-

在 8 位数据线模式下:

-

HS400 模式(200MHz DDR),理论最高数据率可达 400MB/s

-

HS200 模式(200MHz SDR),最高数据率 200MB/s

-

DDR52 模式(52MHz DDR),最高数据率 104MB/s

-

-

支持 1 位/4 位/8 位数据线模式传输

-

-

SD3.0 接口

-

兼容 SD3.0

-

1 个 SD 接口,可配置为 SD/MMC/SDIO

-

最高数据传输带宽 100MB/s

-

支持1 位/4 位数据线传输模式

-

-

图像处理单元

-

支持APIs:

-

支持Vulkan1.1/1.2

-

支持OpenCL1.1/1.2/2.0

-

支持OpenGLES3.0/3.1/3.2

-

-

基于分片的 3D 图形渲染,支持多个分片同时处理

-

可编程的高质量抗混叠

-

支持和 NNA 的 AI 协同

-

先进的 DMA 操作,降低主 CPU 负载

-

压缩纹理编码

-

无损数据压缩

-

固件执行专用处理器

-

性能

-

支持3D 图形加速引擎,3200Mpixel/sec@800MHz

-

F32 操作,每个时钟周期 64 次

-

F16 操作,每个时钟周期 128 次

-

整数操作,每个时钟周期 32 次

-

几何操作,每 4 个时钟周期 1 次三角形操作

-

二维图像加速器

-

输入与输出

-

支持 8/10 位 YUV 4:2:2/YUV 4:2:0 输入输出�格式

-

支持 RGB444/RGB565/RGB888/RGB101010 输入输出格式

-

支持 ARGB4444/ARGB1555/ARGB8888/ARGB2101010 输入输出格式

-

输入输出数据存储格式与 ISP/VENC/VDEC/NPU/DPU/GPU 等适配

-

-

2D操作

-

bitBlit

-

stretchBlit

-

rect fill & clear

-

filterblit

-

Alpha Blending

-

90/180/270 rotation

-

scale/crop

-

line

-

RGB2YUV

-

YUV2RGB

-

-

Multi-src blit

-

支持不同尺寸 rect 多源混叠

-

支持最多 8 个源

-

支持每个源设置单独的旋转参数

-

支持每个源设置单独的缩放参数

-

数字信号处理器

-

支持 2 路独立 DSP 核,主频 1GHz

-

支持 256 个 8x8 MAC

-

支持 16 个单精度 VFPU

-

支持图像直方图统计

-

32KB 指令 Cache

-

2 个 128KB 数据 RAM

-

操作类型

-

加载和存储

-

乘法运算

-

除法运算

-

矢量压缩和扩展

-

算术运算

-

位逻辑运算

-

位操作

-

比较运算

-

移�位作业

-

旋转操作

-

递减操作

-

打包操作

-

选择和双重选择操作

-

随机混合操作

-

移动操作

-

系统组件

-

CRU

-

支持外部晶振 24MHz 输入、外部晶振 32.768KHz 输入、内置 24MHz~26MHz RC

-

支持时钟分频、时钟切换、时钟门控

-

支持上电复位

-

支持外部复位

-

支持看门狗复位

-

支持全局软复位和模块软复位

-

-

PMU

-

支持正常运行模式,空闲模式,HW-VAD 模式,休眠模式

-

支持时钟门控和电源关断

-

支持唤醒源:HW-VAD,RTC and GPIO(键盘,wifi…)

-

支持 4 个独立电源域,可以从外部用 PMIC 关断

-

芯片内部做了隔离保护,以支持电源开关

-

-

中断

-

芯片中集成的每个 CPU 核内部都带有各自的中断控制器

-

E902/C906 CPU 中集成的是与 RISC-V 标准兼容的核内局部中断控制器:CLIC

-

C910 中集成的是与RIISC-V 标准兼容的平台级别中断控制器:PLIC

-

所有中断使用电平触发的方式,高电平有效

-

-

DMAC

-

独立的核、从接口和主接口时钟

-

可以配置 4 个通道,每个通道是一个源和目标对

-

通道优先级可编程

-

DMA 数据传输有四种:内存到内存、内存到外设、外设到内存和外设到外设

-

可编程多块传输,通过链表、连续地址、自动重载和影子寄存器等方式

-

中断触发源包括:

-

DMA 传输完成

-

块传输完成

-

单个或多个事务完成

-

出错

-

通道挂起或禁用

-

-

支持中断使能和屏蔽

-

-

安全引擎

-

TEE+REE 两层安全体系架构

-

硬件随机数发生器

-

基于硬件的隔离机制

-

支持安全启动

-

内置 Sensor 为安全电路提供物理防护

-

支持 ID2 安全芯片能力

-

-

核间通讯

-

支持软件控制的单发单收、多发单收、单发多收、多发多收的多核通信

-

支持发送 CPU 向接收 CPU 传递除中断事件外的信息量,以信息寄存器组的方式体现

-

支持软件查询中断状态,即软件查询当前通信状态

-

支持软件屏蔽中断产生,即软件切断该通信通道

-

支持软件清除中断状态(结束一次通信的必备条件)

-

支持发送方 CPU 传递的信息量(32bit 寄存器个数)为 8

-

视频编解码器

-

视频解码器

-

实时解码器,支持 H.265/H.264/VP9/8/7/6/AVS/AVS+/AVS2.0/VC1/MPEG4

-

支持 H.264 BP/MP/HP@level5.1 解码,最大 4K 分辨率

-

支持 H.265/HEVC Main Profile@level5.1 解码,最大 4K 分辨率

-

支持 VP9 Profile-2 解码,最大 4K 分辨率

-

支持 AVS2.0 解码,最大 4K 分辨率

-

支持 VP6/7/8/AVS/AVS+/VC1/MPEG4 解码,最大 1920x1080 分辨率

-

解码性能最大 4K@120fps

-

-

视频编码器

-

支持 H.264BP/MP/HP@level4.2 编码,最大 4K 分辨率

-

支持 H.265/HEVCMain Profile 编码,最大 4K 分辨率

-

仅支持 I 帧和 P 帧

-

编码性能最大 4K@60fps

-

支持多路编码和多路解码

-

支持编解码同时进行

-

-

JPEG 视频编解码

-

支持 MJPEG/JPEG Baseline 编解码

-

最大支持 32Kx32K JPEG 解码

-

最大支持 16Kx16K JPEG 编码

-

视频接口

-

视频输入接口

-

2 路 2-lanes MIPI CSI-2 输入,每 lane 支持 2.5Gbit/s

-

2 路 2-lanes MIPI CSI-2 可以拼接成 1 路 4-lanes MIPI CSI-2

-

2 路 MIPI 输入可以映射到 2 个 ISP 上或 DMA 上

-

支持 RAW8,RAW10,RAW12 输入格式

-

2-lanes MIPI CSI 支持最大 8MP sensor 输入

-

支持对��单曝光 sensor 的低成本 HDR 算法处理

-

-

视频输出接口

-

16-/24-bit RGB 数字接口输出,最高支持 1080p@30fps

-

2路 4-lanes MIPI DSI 输出,每 lane 支持 2.5Gbit/s HDMI 接口,最高支持 4K@60fps

-

支持 HDMI 2.0,向后兼容 HDMI 1.4

-

最高支持 1080p@120fps,或者 4Kx2K@60fps

-

输入参考时钟 13.5MHz 到 600MHz

-

最高总带宽 18Gbps

-

支持 8 声道音频输出

-

支持 CEC(ConsumerElectronicsControl)

-

支持 HPD(HotPlugDetection)

-

-

图像信号处理器

-

支持两路独立 ISP 处理

-

支持 RAW 8~16 位输入,支持 IR 10 位/YUV420 8 位/RGB888 输出

-

支持 RGB Bayer/RGB IR pattern 4x4 输入处理

-

支持最高 13M 像素输入(12M 像素处理)

-

支持 LSC 和 DPC

-

支持 3A(AE/AWB/AF) 算法

-

支持 2D/3D 图像降噪和图像锐化

-

支持颜色增强,高亮抑制,背光补偿,伽马校正等

-

支持抗闪烁

-

支持鱼眼校正

-

支持 HDR 和 WDR

显示处理单元

-

支持双路视频显示,分辨率可达 4K@60fps + 1080p@60fps

-

两路显示共支持 6 层叠加,两路显示层数可灵活配置

-

支持旋转和缩放

-

视频时序产生

-

HSYNC/VSYNC/DE 信号

-

可编程计数器

-

-

显示接口

-

30 位 DATA 和 HSYNC/VSYNC/DE 并行像素输出

-

DPI 24/18/16位

-

R10G10B10 30 位输出

-

-

显示

-

最大显示尺寸:4Kx2K

-

每个显示独立的同步和场消隐信号

-

每个显示独立的伽马和抖动

-

-

输入格式

-

ARGB2101010,A/XRGB8888,A/XRGB1555,RGB565,A/XRGB4444

-

YUV422,YUV420

-

-

格式转换

-

可从多个 RGB/YUV 格式输入像素

-

颜色空间转换 BT.2020 和 BT.709

-

24 位多格式 RGB 像素输出

-

-

输出格式

- RGB101010/DPI_D16CFG1/DPI_D16CFG2/DPI_D16CFG3/DPI_D18CFG1/DPI_D18CFG2/DPI_D24/DPI_D30

-

硬件光标

- 支持 ARGB888 和屏蔽光标

-

颜色

-

独立的抖动查找表

-

独立的伽马校正查找表

-

坐标生成叠加

-

Alpha 混叠:波特-达夫混叠模式

-

-

滤波和缩放

-

垂直和水平缩放

-

可编程滤波

-

音频处理器

-

C906 单核处理器,主频最高 800MHz

-

RV64IMA[FD]C[V] 指令架构

-

5 级单发按序执行流水线

-

一级哈佛结构的指令和数据缓存,大小为 32KB,缓存行为 64B

-

Sv39 内存管理单元,实现虚实地址转换与内存管理

-

支持 AXI4.0 128 位 Master 接口

-

支持核内中断 CLINT 和中断控制器 PLIC

-

可配置的浮点单元和矢量单元

-

SIMD128 处理单元

-

矢量计算单元的主要特征点如下:

-

遵循 RISC- V V 矢量扩展标准(revision 0.7.1)

-

算力可达 4GFlops(@1GHz)

-

支持配置矢量执行单元

-

支持 INT8/INT16/INT32/FP16/FP32 矢量运算

-

支持 segment load、store 指令

-

音频接口

-

支持 1 个 8 通道(4 个 RX 左右声道或者 4 个 TX 左右声道)I2S 接外部 CODEC 音频输入,最高 384kHz

-

支持 3 个 2 通道 I2S/PCM 接外部 CODEC 播放/录音(16k/32k/48k/44.1k/64k/192k/384kHz) 或蓝牙语音连接 (8k/16k/32k/48k/44.1kHz)

-

支持低功耗 VAD(仅 RX),最大支持 8 通道(4 个 RX 左右声道) I2S

-

支持 8 路(4 个 RX 左右声道) PDM 数据对接外部 DMIC

-

支持 8 路 TDM/PCM 输入

-

支持 2 个 SPDF-IN/OUT,支持采样率 32/44.1/48/88.2/96/192kHz

外设接口

-

GMAC

-

支持 2 路千兆以太网

-

支持 10/100/1000Mbps 数据传输率 RGMII/RMII 接口

-

支持全双工和半双工模式

-

-

USB

-

支持一路 USB3.0 DRD,可作为主机或设备,兼容 USB2.0

-

USB3.0 特性

-

支持 PIPE3 接口

-

5Gbps 数据传输速率

-

自适应接收均衡

-

-

USB2.0 特性

-

支持 UTMI+ 接口

-

高速 480Mbps

-

全速 12Mbps

-

低速 1.5Mbps(仅主机模式)

-

-

-

UART

-

支持 8 路 UART

-

1 路带流控 UART,最高速率 4Mbps

-

3 路支持红外 UART

-

-

I2C

-

支持 7 位/10 位地址模式

-

支持 9 路 I2C,最高速率 1.7Mbps

-

-

ISO7816

- 支持 1 路 ISO7816

-

GPIO

-

支持 145 个 GPIO

-

支持中断

-

-

定时器

-

多达 4 个定时器单元

-

通过配置相关的 sysreg 寄存器,4 个计数器可以成对级联

-

每个定时器可配置定时器宽度:32 位

-

可配置计数器级联��,最大计数位宽可达 128 位

-

支持自由运行和用户自定义计数两种操作模式

-

-

PWM

-

支持 1 路 6 通道 PWM,最高频率 12MHz

-

占空比可配置

-

支持单次模式和连续模式

-

支持单次模式下的事件触发模式

-

-

看门狗

-

可配置 WDT 计数器宽度为 32 位

-

计数器从预设值递减计数到 0,表示发生超时

-

可选的外部时钟使能信号来控制计数器的计数速率

-

如果发生超时,看门狗可以执行如下的一个操作:

-

生成系统复位

-

首先产生一个中断,如果在第二个超时发生时服务程序没有清除该中断,则产生一个系统复位

-

-

其他

-

EFUSE

-

8Kbit 容量

-

编程时间: 5 μs±10%

-

系统框图

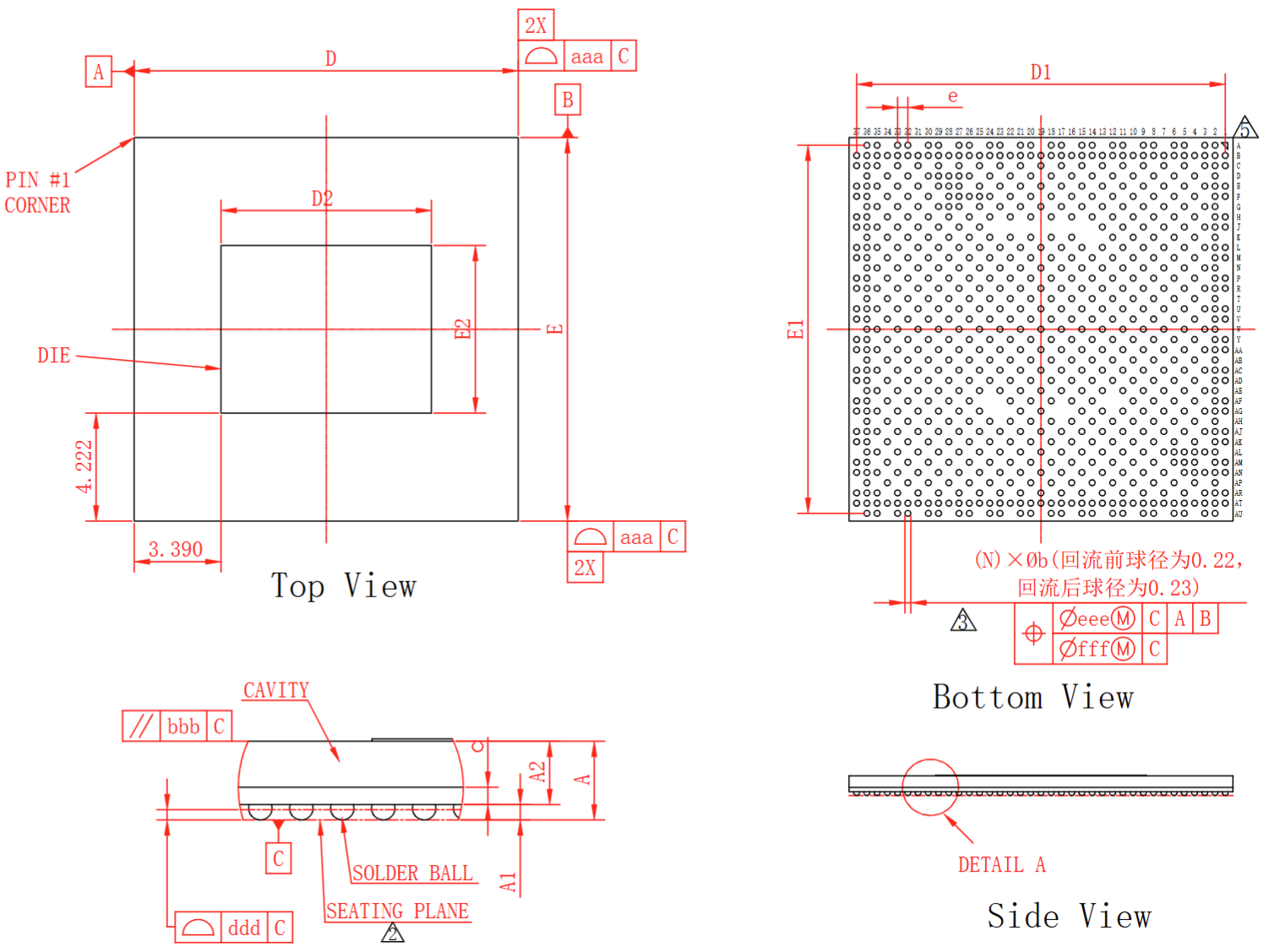

封装信息

封装参数

封装主要参数如下

| 参数 | 值 |

|---|---|

| 形式 | Exposed Die FCCSP |

| 尺寸 | 15 mm×15 mm |

| Ball Number | 777 |

| Ball Size | 0.22 mm |

| Ball Pitch | 0.4 mm |

| 描述 | 矩形阵列,局部镂空 |

| 接口 | DDR (High 32bit),DDR (Low 32bit),eMMC,SDIO,SPI NOR/NAND,USB,GMAC,HDMI,MIPI CSI-2 1 2-Lane,MIPI CSI-2 2 2-Lane,MIPI DSI 0 4-Lane,MIPI DSI 1 4-Lane,UART,I2C,PWM,I2S,SPDIF,GPIO,ISO7816 |

标签

POD 图

| symbol | Dimension in mm | Dimension in inch | ||||

|---|---|---|---|---|---|---|

| MIN | NOM | MAX | MIN | NOM | MAX | |

| A | 0.700 | 0.770 | 0.840 | 0.028 | 0.030 | 0.033 |

| A1 | 0.100 | 0.150 | 0.200 | 0.004 | 0.006 | 0.008 |

| A2 | 0.560 | 0.620 | 0.680 | 0.022 | 0.024 | 0.027 |

| c | 0.140 | 0.170 | 0.200 | 0.006 | 0.007 | 0.008 |

| D | 14.900 | 15.000 | 15.100 | 0.587 | 0.591 | 0.594 |

| E | 14.900 | 15.000 | 15.100 | 0.587 | 0.591 | 0.594 |

| D1 | ---- | 14.400 | ---- | ---- | 0.567 | ---- |

| E1 | ---- | 14.400 | ---- | ---- | 0.567 | ---- |

| D2 | ---- | 8.221 | ---- | ---- | 0.324 | ---- |

| E2 | ---- | 6.556 | ---- | ---- | 0.258 | ---- |

| e | ---- | 0.400 | ---- | ---- | 0.016 | ---- |

| b | 0.180 | 0.230 | 0.280 | 0.007 | 0.009 | 0.011 |

| aaa | 0.100 | 0.004 | ||||

| bbb | 0.100 | 0.004 | ||||

| ddd | 0.100 | 0.004 | ||||

| eee | 0.150 | 0.006 | ||||

| ffff | 0.050 | 0.002 | ||||

热阻参数

| 符号 | 参数 | 典型 | 单位 |

|---|---|---|---|

| θJA | 结到空气环境的热阻,空气流动速度 0m/s | 19.68 | ℃/W |

| θJB | 结到 PCB 的热阻,空气流动速度 0m/s | 1.83 | ℃/W |

| θJC | 结到封装外壳的热阻,空气流动速度 0m/s | 0.05 | ℃/W |

潮敏参数

芯片潮湿敏感等级 MSL 是 3 级。

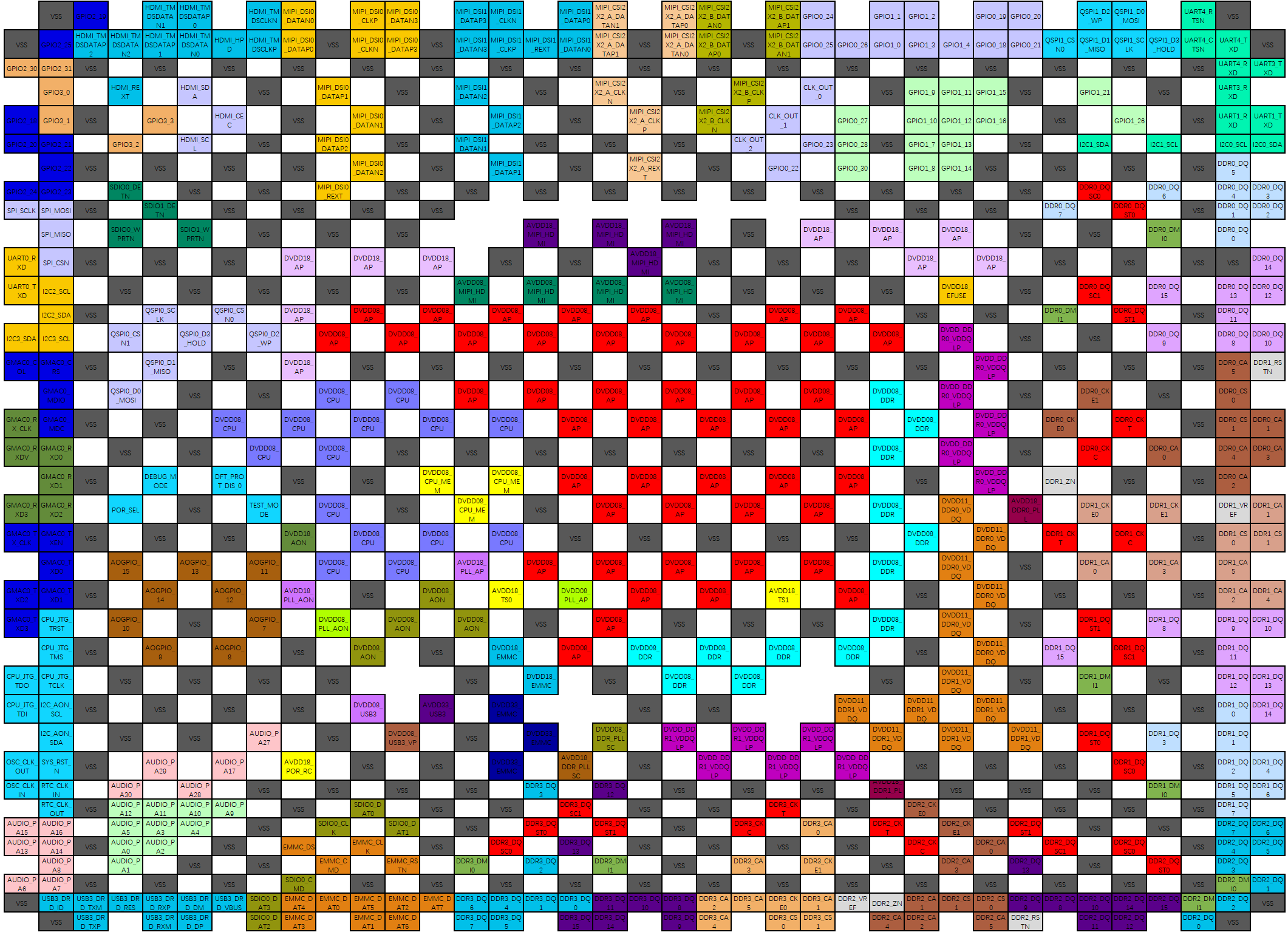

管脚描述

管脚映射图

管脚定义

| 管脚 | 管脚名 | 管脚 | 管脚名 | 管脚 | 管脚名 |

|---|---|---|---|---|---|

| A2 | VSS | AM36 | DDR2_DQ7 | G27 | GPIO1_8 |

| A3 | GPIO2_19 | AM37 | DDR2_DQ6 | G28 | GPIO1_14 |

| A5 | HDMI_TMDSDATAN1 | AN1 | AUDIO_PA13 | G29 | VSS |

| A6 | HDMI_TMDSDATAP0 | AN2 | AUDIO_PA14 | G31 | VSS |

| A8 | HDMI_TMDSCLKN | AN3 | VSS | G33 | VSS |

| A9 | MIPI_DSI0_DATAN0 | AN4 | AUDIO_PA0 | G35 | VSS |

| A11 | MIPI_DSI0_CLKP | AN5 | AUDIO_PA2 | G36 | DDR0_DQ5 |

| A12 | MIPI_DSI0_DATAN3 | AN7 | VSS | H1 | GPIO2_24 |

| A14 | MIPI_DSI1_DATAP3 | AN9 | EMMC_DS | H2 | GPIO2_23 |

| A15 | MIPI_DSI1_CLKN | AN11 | EMMC_CLK | H4 | SDIO0_DETN |

| A17 | MIPI_DSI1_DATAP0 | AN13 | VSS | H6 | VSS |

| A18 | MIPI_CSI2X2_A_DATAN1 | AN15 | DDR3_DQSC0 | H8 | VSS |

| A20 | MIPI_CSI2X2_A_DATAP0 | AN17 | DDR3_DQ13 | H10 | MIPI_DSI0_REXT |

| A21 | MIPI_CSI2X2_B_DATAN0 | AN19 | VSS | H12 | VSS |

| A23 | MIPI_CSI2X2_B_DATAP1 | AN21 | VSS | H14 | VSS |

| A24 | GPIO0_24 | AN23 | VSS | H16 | VSS |

| A26 | GPIO1_1 | AN25 | VSS | H18 | VSS |

| A27 | GPIO1_2 | AN27 | DDR2_CKC | H20 | VSS |

| A29 | GPIO0_19 | AN29 | DDR2_CA0 | H22 | VSS |

| A30 | GPIO0_20 | AN31 | DDR2_DQSC1 | H24 | VSS |

| A32 | QSPI1_D2_WP | AN33 | DDR2_DQSC0 | H26 | VSS |

| A33 | QSPI1_D0_MOSI | AN35 | VSS | H28 | VSS |

| A35 | UART4_RTSN | AN36 | DDR2_DQ4 | H30 | VSS |

| A36 | VSS | AN37 | DDR2_DQ5 | H32 | DDR0_DQSC0 |

| AA1 | GMAC0_TX_CLK | AP2 | AUDIO_PA8 | H34 | DDR0_DQ6 |

| AA2 | GMAC0_TXEN | AP4 | AUDIO_PA1 | H36 | DDR0_DQ4 |

| AA3 | VSS | AP6 | VSS | H37 | DDR0_DQ3 |

| AA5 | VSS | AP8 | VSS | J1 | SPI_SCLK |

| AA7 | VSS | AP10 | EMMC_CMD | J2 | SPI_MOSI |

| AA9 | DVDD18_AON | AP12 | EMMC_RSTN | J3 | VSS |

| AA11 | DVDD08_CPU | AP14 | DDR3_DMI0 | J5 | SDIO1_DETN |

| AA13 | DVDD08_CPU | AP16 | DDR3_DQ2 | J7 | VSS |

| AA15 | DVDD08_CPU | AP18 | DDR3_DMI1 | J9 | VSS |

| AA17 | VSS | AP20 | VSS | J11 | VSS |

| AA19 | VSS | AP22 | DDR3_CA3 | J13 | VSS |

| AA21 | VSS | AP24 | DDR3_CKE1 | J25 | VSS |

| AA23 | VSS | AP26 | VSS | J27 | VSS |

| AA25 | VSS | AP28 | DDR2_CA3 | J29 | VSS |

| AA27 | DVDD08_DDR | AP30 | DDR2_DQ13 | J31 | DDR0_DQ7 |

| AA29 | DVDD11_DDR0_VDDQ | AP32 | VSS | J33 | DDR0_DQST0 |

| AA31 | DDR1_CKT | AP34 | DDR2_DQST0 | J35 | VSS |

| AA33 | DDR1_CKC | AP36 | DDR2_DQ3 | J36 | DDR0_DQ1 |

| AA35 | VSS | AR1 | AUDIO_PA6 | J37 | DDR0_DQ2 |

| AA36 | DDR1_CS0 | AR2 | AUDIO_PA7 | K2 | SPI_MISO |

| AA37 | DDR1_CS1 | AR3 | VSS | K4 | SDIO0_WPRTN |

| AB2 | GMAC0_TXD0 | AR5 | VSS | K6 | SDIO1_WPRTN |

| AB4 | AOGPIO_15 | AR7 | VSS | K8 | VSS |

| AB6 | AOGPIO_13 | AR9 | SDIO0_CMD | K10 | VSS |

| AB8 | AOGPIO_11 | AR11 | VSS | K12 | VSS |

| AB10 | DVDD08_CPU | AR13 | VSS | K16 | AVDD18_MIPI_HDMI |

| AB12 | DVDD08_CPU | AR15 | VSS | K18 | AVDD18_MIPI_HDMI |

| AB14 | AVDD18_PLL_AP | AR17 | VSS | K20 | AVDD18_MIPI_HDMI |

| AB16 | DVDD08_AP | AR19 | VSS | K22 | VSS |

| AB18 | DVDD08_AP | AR21 | VSS | K24 | DVDD18_AP |

| AB20 | DVDD08_AP | AR23 | VSS | K26 | DVDD18_AP |

| AB22 | DVDD08_AP | AR25 | VSS | K28 | DVDD18_AP |

| AB24 | DVDD08_AP | AR27 | VSS | K30 | VSS |

| AB26 | DVDD08_DDR | AR29 | VSS | K32 | VSS |

| AB28 | DVDD11_DDR0_VDDQ | AR31 | VSS | K34 | DDR0_DMI0 |

| AB30 | VSS | AR33 | VSS | K36 | DDR0_DQ0 |

| AB32 | DDR1_CA0 | AR35 | VSS | L1 | UART0_RXD |

| AB34 | DDR1_CA3 | AR36 | DDR2_DMI0 | L2 | SPI_CSN |

| AB36 | DDR1_CA5 | AR37 | DDR2_DQ1 | L3 | VSS |

| AC1 | GMAC0_TXD2 | AT1 | VSS | L5 | VSS |

| AC2 | GMAC0_TXD1 | AT2 | USB3_DRD_ID | L7 | VSS |

| AC3 | VSS | AT3 | USB3_DRD_TXM | L9 | DVDD18_AP |

| AC5 | AOGPIO_14 | AT4 | USB3_DRD_RES | L11 | DVDD18_AP |

| AC7 | AOGPIO_12 | AT5 | USB3_DRD_RXP | L13 | DVDD18_AP |

| AC9 | AVDD18_PLL_AON | AT6 | USB3_DRD_DM | L15 | VSS |

| AC11 | VSS | AT7 | USB3_DRD_VBUS | L17 | VSS |

| AC13 | DVDD08_AON | AT8 | SDIO0_DAT3 | L19 | AVDD18_MIPI_HDMI |

| AC15 | AVDD18_TS0 | AT9 | EMMC_DAT4 | L21 | VSS |

| AC17 | DVDD08_PLL_AP | AT10 | EMMC_DAT0 | L23 | VSS |

| AC19 | DVDD08_AP | AT11 | EMMC_DAT5 | L25 | VSS |

| AC21 | DVDD08_AP | AT12 | EMMC_DAT2 | L27 | DVDD18_AP |

| AC23 | AVDD18_TS1 | AT13 | EMMC_DAT7 | L29 | DVDD18_AP |

| AC25 | DVDD08_AP | AT14 | DDR3_DQ6 | L31 | VSS |

| AC27 | VSS | AT15 | DDR3_DQ4 | L33 | VSS |

| AC29 | DVDD11_DDR0_VDDQ | AT16 | DDR3_DQ1 | L35 | VSS |

| AC31 | VSS | AT17 | DDR3_DQ0 | L36 | VSS |

| AC33 | VSS | AT18 | DDR3_DQ11 | L37 | DDR0_DQ14 |

| AC35 | VSS | AT19 | DDR3_DQ10 | M1 | UART0_TXD |

| AC36 | DDR1_CA2 | AT20 | DDR3_DQ8 | M2 | I2C2_SCL |

| AC37 | DDR1_CA4 | AT21 | DDR3_CA2 | M4 | VSS |

| AD1 | GMAC0_TXD3 | AT22 | DDR3_CA5 | M6 | VSS |

| AD2 | CPU_JTG_TRST | AT23 | DDR3_CKE0 | M8 | VSS |

| AD4 | AOGPIO_10 | AT24 | DDR3_CA1 | M10 | VSS |

| AD6 | VSS | AT25 | DDR2_VREF | M12 | VSS |

| AD8 | AOGPIO_7 | AT26 | DDR2_ZN | M14 | AVDD08_MIPI_HDMI |

| AD10 | DVDD08_PLL_AON | AT27 | DDR2_CA1 | M16 | AVDD08_MIPI_HDMI |

| AD12 | DVDD08_AON | AT28 | DDR2_CS1 | M18 | AVDD08_MIPI_HDMI |

| AD14 | DVDD08_AON | AT29 | DDR2_CS0 | M20 | AVDD08_MIPI_HDMI |

| AD16 | VSS | AT30 | DDR2_DQ9 | M22 | VSS |

| AD18 | DVDD08_AP | AT31 | DDR2_DQ8 | M24 | VSS |

| AD20 | VSS | AT32 | DDR2_DQ10 | M26 | VSS |

| AD22 | VSS | AT33 | DDR2_DQ14 | M28 | DVDD18_EFUSE |

| AD24 | VSS | AT34 | DDR2_DQ15 | M30 | VSS |

| AD26 | DVDD08_DDR | AT35 | DDR2_DMI1 | M32 | DDR0_DQSC1 |

| AD28 | DVDD11_DDR0_VDDQ | AT36 | DDR2_DQ2 | M34 | DDR0_DQ15 |

| AD30 | VSS | AT37 | VSS | M36 | DDR0_DQ13 |

| AD32 | DDR1_DQST1 | AU2 | VSS | M37 | DDR0_DQ12 |

| AD34 | DDR1_DQ8 | AU3 | USB3_DRD_TXP | N2 | I2C2_SDA |

| AD36 | DDR1_DQ9 | AU5 | USB3_DRD_RXM | N3 | VSS |

| AD37 | DDR1_DQ10 | AU6 | USB3_DRD_DP | N5 | QSPI0_SCLK |

| AE2 | CPU_JTG_TMS | AU8 | SDIO0_DAT2 | N7 | QSPI0_CSN0 |

| AE3 | VSS | AU9 | EMMC_DAT3 | N9 | DVDD18_AP |

| AE5 | AOGPIO_9 | AU11 | EMMC_DAT1 | N11 | DVDD08_AP |

| AE7 | AOGPIO_8 | AU12 | EMMC_DAT6 | N13 | DVDD08_AP |

| AE9 | VSS | AU14 | DDR3_DQ7 | N15 | DVDD08_AP |

| AE11 | DVDD08_AON | AU15 | DDR3_DQ5 | N17 | DVDD08_AP |

| AE13 | VSS | AU17 | DDR3_DQ15 | N19 | DVDD08_AP |

| AE15 | DVDD18_EMMC | AU18 | DDR3_DQ14 | N21 | VSS |

| AE17 | DVDD08_AP | AU20 | DDR3_DQ9 | N23 | DVDD08_AP |

| AE19 | DVDD08_DDR | AU21 | DDR3_CA4 | N25 | DVDD08_AP |

| AE21 | DVDD08_DDR | AU23 | DDR3_CS0 | N27 | VSS |

| AE23 | DVDD08_DDR | AU24 | DDR3_CS1 | N29 | VSS |

| AE25 | DVDD08_DDR | AU26 | DDR2_CA4 | N31 | DDR0_DMI1 |

| AE27 | VSS | AU27 | DDR2_CA2 | N33 | DDR0_DQST1 |

| AE29 | DVDD11_DDR0_VDDQ | AU29 | DDR2_CA5 | N35 | VSS |

| AE31 | DDR1_DQ15 | AU30 | DDR2_RSTN | N36 | DDR0_DQ11 |

| AE33 | DDR1_DQSC1 | AU32 | DDR2_DQ11 | P1 | I2C3_SDA |

| AE35 | VSS | AU33 | DDR2_DQ12 | P2 | I2C3_SCL |

| AE36 | DDR1_DQ11 | AU35 | DDR2_DQ0 | P4 | QSPI0_CSN1 |

| AF1 | CPU_JTG_TDO | AU36 | VSS | P6 | QSPI0_D3_HOLD |

| AF2 | CPU_JTG_TCLK | B1 | VSS | P8 | QSPI0_D2_WP |

| AF4 | VSS | B2 | GPIO2_25 | P10 | DVDD08_AP |

| AF6 | VSS | B3 | HDMI_TMDSDATAP2 | P12 | DVDD08_AP |

| AF8 | VSS | B4 | HDMI_TMDSDATAN2 | P14 | DVDD08_AP |

| AF10 | VSS | B5 | HDMI_TMDSDATAP1 | P16 | DVDD08_AP |

| AF14 | VSS | B6 | HDMI_TMDSDATAN0 | P18 | DVDD08_AP |

| AF16 | DVDD18_EMMC | B7 | HDMI_HPD | P20 | DVDD08_AP |

| AF18 | VSS | B8 | HDMI_TMDSCLKP | P22 | DVDD08_AP |

| AF20 | DVDD08_DDR | B9 | MIPI_DSI0_DATAP0 | P24 | DVDD08_AP |

| AF22 | DVDD08_DDR | B10 | VSS | P26 | DVDD08_AP |

| AF26 | VSS | B11 | MIPI_DSI0_CLKN | P28 | DVDD_DDR0_VDDQLP |

| AF28 | DVDD11_DDR1_VDDQ | B12 | MIPI_DSI0_DATAP3 | P30 | VSS |

| AF30 | VSS | B13 | VSS | P32 | VSS |

| AF32 | DDR1_DMI1 | B14 | MIPI_DSI1_DATAN3 | P34 | DDR0_DQ9 |

| AF34 | VSS | B15 | MIPI_DSI1_CLKP | P36 | DDR0_DQ8 |

| AF36 | DDR1_DQ12 | B16 | MIPI_DSI1_REXT | P37 | DDR0_DQ10 |

| AF37 | DDR1_DQ13 | B17 | MIPI_DSI1_DATAN0 | R1 | GMAC0_COL |

| AG1 | CPU_JTG_TDI | B18 | MIPI_CSI2X2_A_DATAP1 | R2 | GMAC0_CRS |

| AG2 | I2C_AON_SCL | B19 | VSS | R3 | VSS |

| AG3 | VSS | B20 | MIPI_CSI2X2_A_DATAN0 | R5 | QSPI0_D1_MISO |

| AG5 | VSS | B21 | MIPI_CSI2X2_B_DATAP0 | R7 | VSS |

| AG7 | VSS | B22 | VSS | R9 | DVDD18_AP |

| AG9 | VSS | B23 | MIPI_CSI2X2_B_DATAN1 | R11 | VSS |

| AG11 | DVDD08_USB3 | B24 | GPIO0_25 | R13 | VSS |

| AG13 | AVDD33_USB3 | B25 | GPIO0_26 | R15 | VSS |

| AG15 | DVDD33_EMMC | B26 | GPIO1_0 | R17 | VSS |

| AG19 | VSS | B27 | GPIO1_3 | R19 | VSS |

| AG21 | VSS | B28 | GPIO1_4 | R21 | VSS |

| AG25 | DVDD11_DDR1_VDDQ | B29 | GPIO0_18 | R23 | VSS |

| AG27 | DVDD11_DDR1_VDDQ | B30 | GPIO0_21 | R25 | VSS |

| AG29 | DVDD11_DDR1_VDDQ | B31 | QSPI1_CSN0 | R27 | VSS |

| AG31 | VSS | B32 | QSPI1_D1_MISO | R29 | DVDD_DDR0_VDDQLP |

| AG33 | VSS | B33 | QSPI1_SCLK | R31 | VSS |

| AG35 | VSS | B34 | QSPI1_D3_HOLD | R33 | VSS |

| AG36 | DDR1_DQ0 | B35 | UART4_CTSN | R35 | VSS |

| AG37 | DDR1_DQ14 | B36 | UART4_TXD | R36 | DDR0_CA5 |

| AH2 | I2C_AON_SDA | B37 | VSS | R37 | DDR1_RSTN |

| AH4 | VSS | C1 | GPIO2_30 | T2 | GMAC0_MDIO |

| AH6 | VSS | C2 | GPIO2_31 | T4 | QSPI0_D0_MOSI |

| AH8 | AUDIO_PA27 | C3 | VSS | T6 | VSS |

| AH10 | VSS | C5 | VSS | T8 | VSS |

| AH12 | DVDD08_USB3_VP | C7 | VSS | T10 | DVDD08_CPU |

| AH14 | VSS | C9 | VSS | T12 | DVDD08_CPU |

| AH16 | DVDD33_EMMC | C11 | VSS | T14 | DVDD08_AP |

| AH18 | DVDD08_DDR_PLLSC | C13 | VSS | T16 | DVDD08_AP |

| AH20 | DVDD_DDR1_VDDQLP | C15 | VSS | T18 | DVDD08_AP |

| AH22 | DVDD_DDR1_VDDQLP | C17 | VSS | T20 | DVDD08_AP |

| AH24 | DVDD_DDR1_VDDQLP | C19 | VSS | T22 | DVDD08_AP |

| AH26 | DVDD11_DDR1_VDDQ | C21 | VSS | T24 | DVDD08_AP |

| AH28 | DVDD11_DDR1_VDDQ | C23 | VSS | T26 | DVDD08_DDR |

| AH30 | DVDD11_DDR1_VDDQ | C25 | VSS | T28 | DVDD_DDR0_VDDQLP |

| AH32 | DDR1_DQST0 | C27 | VSS | T30 | VSS |

| AH34 | DDR1_DQ3 | C29 | VSS | T32 | DDR0_CKE1 |

| AH36 | DDR1_DQ1 | C31 | VSS | T34 | VSS |

| AJ1 | OSC_CLK_OUT | C33 | VSS | T36 | DDR0_CS0 |

| AJ2 | SYS_RST_N | C35 | VSS | U1 | GMAC0_RX_CLK |

| AJ3 | VSS | C36 | UART4_RXD | U2 | GMAC0_MDC |

| AJ5 | AUDIO_PA29 | C37 | UART3_TXD | U3 | VSS |

| AJ7 | AUDIO_PA17 | D2 | GPIO3_0 | U5 | VSS |

| AJ9 | AVDD18_POR_RC | D4 | HDMI_REXT | U7 | DVDD08_CPU |

| AJ11 | VSS | D6 | HDMI_SDA | U9 | DVDD08_CPU |

| AJ13 | VSS | D8 | VSS | U11 | DVDD08_CPU |

| AJ15 | DVDD33_EMMC | D10 | MIPI_DSI0_DATAP1 | U13 | DVDD08_CPU |

| AJ17 | AVDD18_DDR_PLLSC | D12 | VSS | U15 | DVDD08_CPU |

| AJ19 | VSS | D14 | MIPI_DSI1_DATAN2 | U17 | DVDD08_AP |

| AJ21 | DVDD_DDR1_VDDQLP | D16 | VSS | U19 | DVDD08_AP |

| AJ23 | DVDD_DDR1_VDDQLP | D18 | MIPI_CSI2X2_A_CLKN | U21 | DVDD08_AP |

| AJ25 | DVDD_DDR1_VDDQLP | D20 | VSS | U23 | DVDD08_AP |

| AJ27 | VSS | D22 | MIPI_CSI2X2_B_CLKP | U25 | DVDD08_AP |

| AJ29 | VSS | D24 | CLK_OUT_0 | U27 | DVDD08_DDR |

| AJ31 | VSS | D26 | VSS | U29 | DVDD_DDR0_VDDQLP |

| AJ33 | DDR1_DQSC0 | D27 | GPIO1_9 | U31 | DDR0_CKE0 |

| AJ35 | VSS | D28 | GPIO1_11 | U33 | DDR0_CKT |

| AJ36 | DDR1_DQ2 | D29 | GPIO1_15 | U35 | VSS |

| AJ37 | DDR1_DQ4 | D30 | VSS | U36 | DDR0_CS1 |

| AK1 | OSC_CLK_IN | D32 | GPIO1_21 | U37 | DDR0_CA1 |

| AK2 | RTC_CLK_IN | D34 | VSS | V1 | GMAC0_RXDV |

| AK4 | AUDIO_PA30 | D36 | UART3_RXD | V2 | GMAC0_RXD0 |

| AK6 | AUDIO_PA28 | E1 | GPIO2_18 | V4 | VSS |

| AK8 | VSS | E2 | GPIO3_1 | V6 | VSS |

| AK10 | VSS | E3 | VSS | V8 | DVDD08_CPU |

| AK12 | VSS | E5 | GPIO3_3 | V10 | DVDD08_CPU |

| AK14 | VSS | E7 | HDMI_CEC | V12 | VSS |

| AK16 | DDR3_DQ3 | E9 | VSS | V14 | VSS |

| AK18 | DDR3_DQ12 | E11 | MIPI_DSI0_DATAN1 | V16 | VSS |

| AK20 | VSS | E13 | VSS | V18 | VSS |

| AK22 | VSS | E15 | MIPI_DSI1_DATAP2 | V20 | VSS |

| AK24 | VSS | E17 | VSS | V22 | VSS |

| AK26 | AVDD18_DDR1_PLL | E19 | MIPI_CSI2X2_A_CLKP | V24 | VSS |

| AK28 | VSS | E21 | MIPI_CSI2X2_B_CLKN | V26 | DVDD08_DDR |

| AK30 | VSS | E23 | CLK_OUT_1 | V28 | DVDD_DDR0_VDDQLP |

| AK32 | VSS | E25 | GPIO0_27 | V30 | VSS |

| AK34 | DDR1_DMI0 | E27 | GPIO1_10 | V32 | DDR0_CKC |

| AK36 | DDR1_DQ5 | E28 | GPIO1_12 | V34 | DDR0_CA0 |

| AK37 | DDR1_DQ6 | E29 | GPIO1_16 | V36 | DDR0_CA4 |

| AL2 | RTC_CLK_OUT | E31 | VSS | V37 | DDR0_CA3 |

| AL3 | VSS | E33 | GPIO1_26 | W2 | GMAC0_RXD1 |

| AL4 | AUDIO_PA12 | E35 | VSS | W3 | VSS |

| AL5 | AUDIO_PA11 | E36 | UART1_RXD | W5 | DEBUG_MODE |

| AL6 | AUDIO_PA10 | E37 | UART1_TXD | W7 | DFT_PROT_DIS_0 |

| AL7 | AUDIO_PA9 | F1 | GPIO2_20 | W9 | VSS |

| AL9 | VSS | F2 | GPIO2_21 | W11 | VSS |

| AL11 | SDIO0_DAT0 | F4 | GPIO3_2 | W13 | DVDD08_CPU_MEM |

| AL13 | VSS | F6 | HDMI_SCL | W15 | DVDD08_CPU_MEM |

| AL15 | VSS | F8 | VSS | W17 | DVDD08_AP |

| AL17 | DDR3_DQSC1 | F10 | MIPI_DSI0_DATAP2 | W19 | DVDD08_AP |

| AL19 | VSS | F12 | VSS | W21 | DVDD08_AP |

| AL21 | VSS | F14 | MIPI_DSI1_DATAN1 | W23 | DVDD08_AP |

| AL23 | DDR3_CKT | F16 | VSS | W25 | DVDD08_AP |

| AL25 | VSS | F18 | VSS | W27 | VSS |

| AL27 | DDR2_CKE0 | F20 | VSS | W29 | DVDD_DDR0_VDDQLP |

| AL29 | VSS | F22 | CLK_OUT_2 | W31 | DDR1_ZN |

| AL31 | VSS | F24 | GPIO0_23 | W33 | VSS |

| AL33 | VSS | F25 | GPIO0_28 | W35 | VSS |

| AL35 | VSS | F26 | VSS | W36 | DDR0_CA2 |

| AL36 | DDR1_DQ7 | F27 | GPIO1_7 | Y1 | GMAC0_RXD3 |

| AM1 | AUDIO_PA15 | F28 | GPIO1_13 | Y2 | GMAC0_RXD2 |

| AM2 | AUDIO_PA16 | F30 | VSS | Y4 | POR_SEL |

| AM4 | AUDIO_PA5 | F32 | I2C1_SDA | Y6 | VSS |

| AM5 | AUDIO_PA3 | F34 | I2C1_SCL | Y8 | TEST_MODE |

| AM6 | AUDIO_PA4 | F36 | I2C0_SCL | Y10 | DVDD08_CPU |

| AM8 | VSS | F37 | I2C0_SDA | Y12 | VSS |

| AM10 | SDIO0_CLK | G2 | GPIO2_22 | Y14 | DVDD08_CPU_MEM |

| AM12 | SDIO0_DAT1 | G3 | VSS | Y16 | VSS |

| AM14 | VSS | G5 | VSS | Y18 | DVDD08_AP |

| AM16 | DDR3_DQST0 | G7 | VSS | Y20 | DVDD08_AP |

| AM18 | DDR3_DQST1 | G9 | VSS | Y22 | DVDD08_AP |

| AM20 | VSS | G11 | MIPI_DSI0_DATAN2 | Y24 | DVDD08_AP |

| AM22 | DDR3_CKC | G13 | VSS | Y26 | DVDD08_DDR |

| AM24 | DDR3_CA0 | G15 | MIPI_DSI1_DATAP1 | Y28 | DVDD11_DDR0_VDDQ |

| AM26 | DDR2_CKT | G17 | VSS | Y30 | AVDD18_DDR0_PLL |

| AM28 | DDR2_CKE1 | G19 | MIPI_CSI2X2_A_REXT | Y32 | DDR1_CKE0 |

| AM30 | DDR2_DQST1 | G21 | VSS | Y34 | DDR1_CKE1 |

| AM32 | VSS | G23 | GPIO0_22 | Y36 | DDR1_VREF |

| AM34 | VSS | G25 | GPIO0_30 | Y37 | DDR1_CA1 |

上下电时序

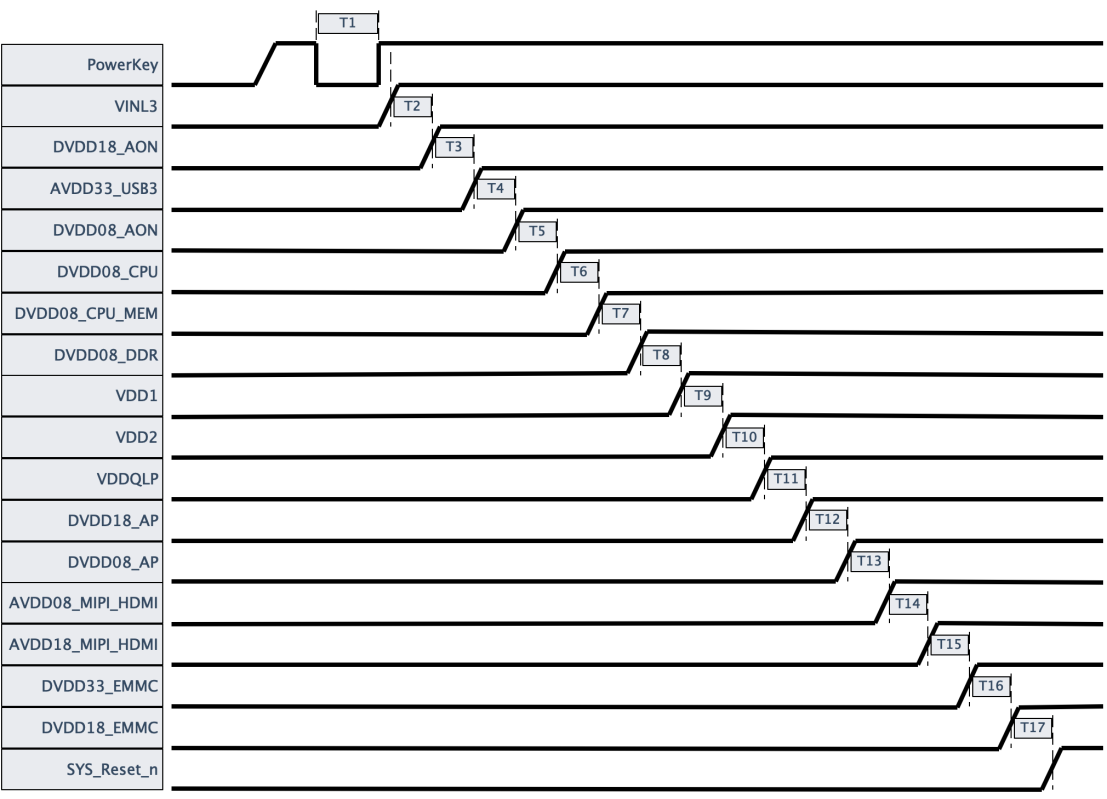

上电时序

上电时序图如下所示。

上电时参数如下所示。

| 符号 | 参数 | 最小 | 典型 | 最大 | 单位 |

|---|---|---|---|---|---|

| T1 | PowerKey 有效时间 | - | 1000 | - | ms |

| T2 | VINL3 有效到 DVDD18_AON 有效的时间间隔 | - | 2 | - | ms |

| T3 | DVDD18_AON 有效到 AVDD33_USB3 有效的时间间隔 | - | 2 | - | ms |

| T4 | AVDD33_USB3 有效到 DVDD08_AON 有效的时间间隔 | - | 2 | - | ms |

| T5 | DVDD08_AON 有效到 DVDD08_CPU 有效的时间间隔 | - | 2 | - | ms |

| T6 | DVDD08_CPU 有效到 DVDD08_CPU_MEM 有效的时间间隔 | - | 2 | - | ms |

| T7 | DVDD08_CPU_MEM 有效到 DVDD08_DDR 有效的时间间隔 | 0 | 50 | - | us |

| T8 | DVDD08_DDR 有效到 VDD1 有效的时间间隔 | 0 | 50 | - | us |

| T9 | VDD1 有效到 VDD2 有效的时间间隔 | - | 2 | - | ms |

| T10 | VDD2 有效到 VDDQLP 有效的时间间隔 | - | 2 | - | ms |

| T11 | VDDQLP 有效到 DVDD18_AP 有效的时间间隔 | 0 | 50 | - | us |

| T12 | DVDD18_AP 有效到 DVDD08_AP 有效的时间间隔 | - | 4 | - | ms |

| T13 | DVDD08_A 有效到 AVDD08_MIPI_HDMI 有效的时间间隔 | - | 2 | - | ms |

| T14 | AVDD08_MIPI_HDMI 有效到 AVDD18_MIPI_HDMI 有效的时间间隔 | 0 | 50 | - | us |

| T15 | AVDD18_MIPI_HDMI 有效到 DVDD33_EMMC 有效的时间间隔 | 0 | 50 | - | us |

| T16 | DVDD33_EMMC 有效到 DVDD18_EMMC 有效的时间间隔 | 0 | 50 | - | us |

| T17 | DVDD18_EMMC 有效到 SYS_Reset_n 释放的时间间隔 | 4 | 6 | - | ms |

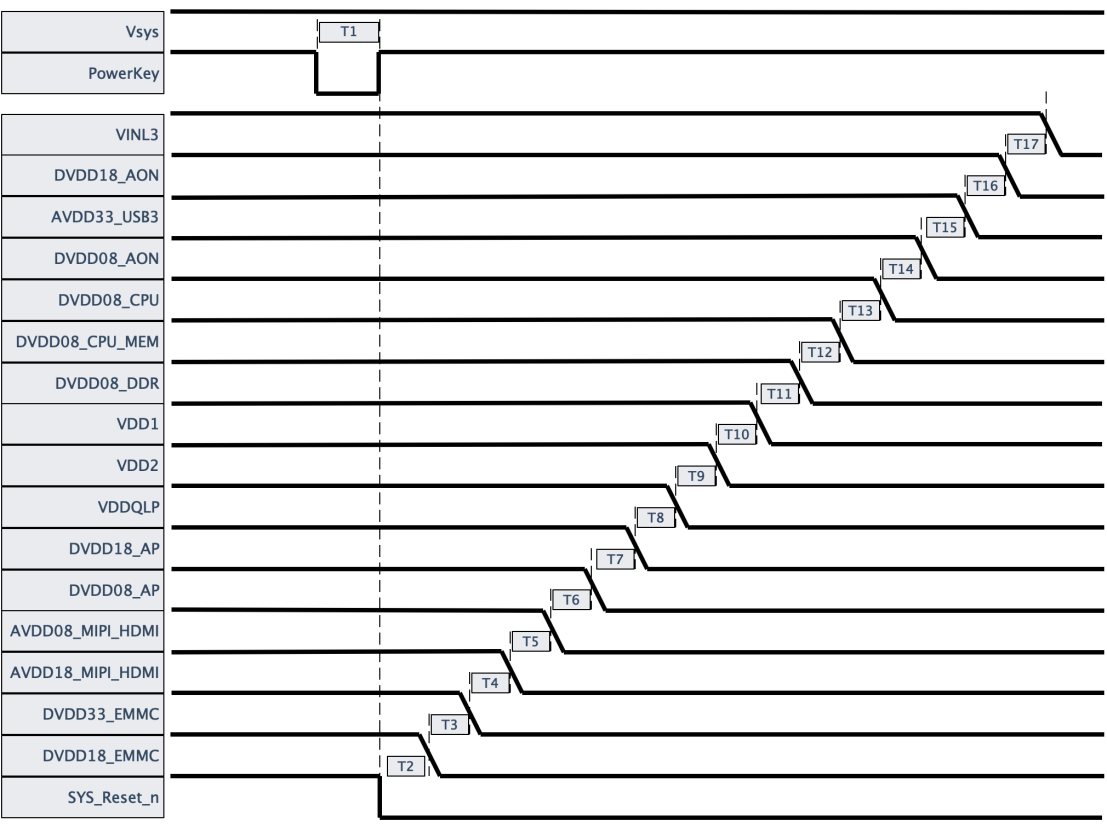

下电时序

下电时序图如下所示。

下电时参数如下所示。

| 符号 | 参数 | 最小 | 典型 | 最大 | 单位 |

|---|---|---|---|---|---|

| T1 | PowerKey 有效时间 | - | 1000 | - | ms |

| T2 | SYS_Reset_n 置位到 DVDD18_EMMC 下电的时间间隔 | 4 | 6 | - | ms |

| T3 | DVDD18_EMMC 下电到 DVDD33_EMMC 下电的时间间隔 | 0 | 50 | - | us |

| T4 | DVDD33_EMMC 下电到 AVDD18_MIPI_HDMI 下电的时间间隔 | 0 | 50 | - | us |

| T5 | AVDD18_MIPI_HDMI 下电到 AVDD08_MIPI_HDMI 下电的时间间隔 | 0 | 50 | - | us |

| T6 | AVDD08_MIPI_HDMI 下电到 DVDD08_AP 下电的时间间隔 | - | 2 | - | ms |

| T7 | DVDD08_AP 下电到 DVDD18_AP 下电的时间间隔 | - | 4 | - | ms |

| T8 | DVDD18_AP 下电到 VDDQLP 下电的时间间隔 | 0 | 50 | - | us |

| T9 | VDDQLP 下电到 VDD2 下电的时间间隔 | 2 | ms | ||

| T10 | VDD2 下电到 VDD1 下电的时间间隔 | 2 | ms | ||

| T11 | VDD1 下电到 DVDD08_DDR 下电的时间间隔 | 0 | 50 | - | us |

| T12 | DVDD08_DDR 下电到 DVDD08_CPU_MEM 下电的时间间隔 | 0 | 50 | - | us |

| T13 | DVDD08_CPU_MEM 下电到 DVDD08_CPU 下电的时间间隔 | - | 2 | - | ms |

| T14 | DVDD08_CPU 下电到 DVDD08_AON 下电的时间间隔 | - | 2 | - | ms |

| T15 | DVDD08_AON 下电到 AVDD33_USB3 下电的时间间隔 | - | 2 | - | ms |

| T16 | AVDD33_USB3 下电到 DVDD18_AON 下电的时间间隔 | - | 2 | - | ms |

| T17 | DVDD18_AON 下电到 VINL3 下电的时间间隔 | - | 2 | - | ms |

电气特性

绝对最大额定值

绝对最大额定值列表如下。

| 符号 | 参数 | 最大 | 单位 |

|---|---|---|---|

| AVDD08_MIPI_HDMI | Analog core power supply for HDMI and MIPI | 0.88 | V |

| AVDD18_ADC | Analog power supply for analog IO | 1.98 | V |

| AVDD18_DDR_PLLSC | Analog power supply for PLL in DDR_SUBSYS | 1.98 | V |

| AVDD18_DDR0_PLL | Analog power supply for VAA of PLL in DDR0 | 1.98 | V |

| AVDD18_DDR1_PLL | Analog power supply for VAA of PLL in DDR1 | 1.98 | V |

| AVDD18_MIPI_HDMI | Analog IO power supply for HDMI and MIPI | 1.98 | V |

| AVDD18_PLL_AON | Analog power supply for PLL in AON power domain | 1.98 | V |

| AVDD18_PLL_AP | Analog power supply for PLL in AP power domain | 1.98 | V |

| AVDD18_POR_RC | Analog power supply for internal POR and RC | 1.98 | V |

| AVDD18_TS_VM | Analog power supply for voltage sensor in AP power domain | 1.98 | V |

| AVDD18_TS0 | Analog power supply for temperature sensor0 in AP power domain | 1.98 | V |

| AVDD18_TS1 | Analog power supply for temperature sensor1 in AP power domain | 1.98 | V |

| AVDD33_USB3 | Analog power supply for USB3 PHY | 3.63 | V |

| DVDD_DDR0_VDDQLP | DDR IO power supply for LP4XDDR IO power supply for LP4 | 0.65 1.17 | V |

| DVDD_DDR1_VDDQLP | DDR IO power supply for LP4XDDR IO power supply for LP4 | 0.65 1.17 | V |

| DVDD08_AON | Digital core power supply for AON power domain | 0.88 | V |

| DVDD08_AP | Digital core power supply for AP power domain | 0.88 | V |

| DVDD08_CPU | Digital core power supply for CPU | 1.05 | V |

| DVDD08_CPU_MEM | Digital core power supply for CPU memory | 1.05 | V |

| DVDD08_DDR | Digital core power supply for DDR controller | 0.88 | V |

| DVDD08_DDR_PLLSC | Digital power supply for PLL in DDR_SUBSYS | 0.88 | V |

| DVDD08_PLL_AON | Digital power supply for PLL in AON power domain | 0.88 | V |

| DVDD08_PLL_AP | Digital power supply for PLL in AP power domain | 0.88 | V |

| DVDD08_USB3 | Power supply for USB3 PHY | 0.88 | V |

| DVDD08_USB3_VP | Power supply for USB3 PHY | 0.88 | V |

| DVDD08_USB3_VPTX0 | Power supply for USB3 PHY transmitter | 0.88 | V |

| DVDD11_DDR0_VDDQ | DDR IO power supply | 1.17 | V |

| DVDD11_DDR1_VDDQ | DDR IO power supply | 1.17 | V |

| DVDD18_AON | Digital power supply for IO in AON power domain | 1.98 | V |

| DVDD18_AP | Digital power supply for IO in AP power domain | 1.98 | V |

| DVDD18_EFUSE | EFUSE programming voltage supply | 1.98 | V |

| DVDD18_EMMC | Power supply for EMMC IO | 1.98 | V |

| DVDD33_EMMC | Power supply for EMMC IO | 3.63 | V |

| VI | Digital I/O input voltage | 1.98 | V |

| TSTORAGE | Storage temperature | 125 | ℃ |

推荐操作条件

推荐操作条件如下。

| 符号 | 参数 | 最小 | 典型 | 最大 | 单位 |

|---|---|---|---|---|---|

| AVDD08_MIPI_HDMI | Analog core power supply for HDMI and MIPI | 0.76 | 0.8 | 0.84 | V |

| AVDD18_ADC | Analog power supply for analog IO | 1.71 | 1.8 | 1.89 | V |

| AVDD18_DDR_PLLSC | Analog power supply for PLL in DDR_SUBSYS | 1.71 | 1.8 | 1.89 | V |

| AVDD18_DDR0_PLL | Analog power supply for VAA of PLL in DDR0 | 1.71 | 1.8 | 1.89 | V |

| AVDD18_DDR1_PLL | Analog power supply for VAA of PLL in DDR1 | 1.71 | 1.8 | 1.89 | V |

| AVDD18_MIPI_HDMI | Analog IO power supply for HDMI and MIPI | 1.71 | 1.8 | 1.89 | V |

| AVDD18_PLL_AON | Analog power supply for PLL in AON power domain | 1.71 | 1.8 | 1.89 | V |

| AVDD18_PLL_AP | Analog power supply for PLL in AP power domain | 1.71 | 1.8 | 1.89 | V |

| AVDD18_POR_RC | Analog power supply for internal POR and RC | 1.71 | 1.8 | 1.89 | V |

| AVDD18_TS_VM | Analog power supply for voltage sensor in AP power domain | 1.71 | 1.8 | 1.89 | V |

| AVDD18_TS0 | Analog power supply for temperature sensor0 in AP power domain | 1.71 | 1.8 | 1.89 | V |

| AVDD18_TS1 | Analog power supply for temperature sensor1 in AP power domain | 1.71 | 1.8 | 1.89 | V |

| AVDD33_USB3 | Analog power supply for USB3 PHY | 3.15 | 3.3 | 3.45 | V |

| DVDD_DDR0_VDDQLP | DDR IO power supply for LP4XDDR IO power supply for LP4 | 0.57 1.06 | 0.6 1.1 | 0.63 1.17 | V |

| DVDD_DDR1_VDDQLP | DDR IO power supply for LP4XDDR IO power supply for LP4 | 0.57 1.06 | 0.6 1.1 | 0.63 1.17 | V |

| DVDD08_AON | Digital core power supply for AON power domain | 0.76 | 0.8 | 0.84 | V |

| DVDD08_AP | Digital core power supply for AP power domain | 0.76 | 0.8 | 0.84 | V |

| DVDD08_CPU | Digital core power supply for CPU | - | 1.0 | 1.05 | V |

| - | 2 | - | GHz | ||

| DVDD08_CPU_MEM | Digital core power supply for CPU | - | 1.0 | 1.05 | V |

| - | 2 | - | GHz | ||

| DVDD08_CPU | Digital core power supply for CPU | 0.95 | 1.0 | 1.05 | V |

| 1.85 | - | - | GHz | ||

| DVDD08_CPU_MEM | Digital core power supply for CPU | 0.95 | 1.0 | 1.05 | V |

| 1.85 | - | - | GHz | ||

| DVDD08_CPU | Digital core power supply for CPU | 0.76 | 0.8 | 0.84 | V |

| 1.5 | - | - | GHz | ||

| DVDD08_CPU_MEM | Digital core power supply for CPU | 0.76 | 0.8 | 0.84 | V |

| 1.5 | - | - | GHz | ||

| DVDD08_CPU | Digital core power supply for CPU | 0.665 | 0.7 | 0.735 | V |

| 800 | - | - | MHz | ||

| DVDD08_CPU_MEM | Digital core power supply for CPU | 0.76 | 0.8 | 0.84 | V |

| 800 | - | - | MHz | ||

| DVDD08_CPU | Digital core power supply for CPU | 0.57 | 0.6 | 0.63 | V |

| 300 | - | - | MHz | ||

| DVDD08_CPU_MEM | Digital core power supply for CPU | 0.71 | 0.75 | 0.79 | V |

| 300 | - | - | MHz | ||

| DVDD08_DDR | Digital core power supply for DDR controller | 0.76 | 0.8 | 0.84 | V |

| DVDD08_DDR_PLLSC | Digital power supply for PLL in DDR_SUBSYS | 0.76 | 0.8 | 0.84 | V |

| DVDD08_PLL_AON | Digital power supply for PLL in AON power domain | 0.76 | 0.8 | 0.84 | V |

| DVDD08_PLL_AP | Digital power supply for PLL in AP power domain | 0.76 | 0.8 | 0.84 | V |

| DVDD08_USB3 | Power supply for USB3 PHY | 0.76 | 0.8 | 0.84 | V |

| DVDD08_USB3_VP | Power supply for USB3 PHY | 0.76 | 0.8 | 0.84 | V |

| DVDD08_USB3_VPTX0 | Power supply for USB3 PHY transmitter | 0.76 | 0.8 | 0.84 | V |

| DVDD11_DDR0_VDDQ | DDR IO power supply | 1.06 | 1.1 | 1.17 | V |

| DVDD11_DDR1_VDDQ | DDR IO power supply | 1.06 | 1.1 | 1.17 | V |

| DVDD18_AON | Digital power supply for IO in AON power domain | 1.71 | 1.8 | 1.89 | V |

| DVDD18_AP | Digital power supply for IO in AP power domain | 1.71 | 1.8 | 1.89 | V |

| DVDD18_EFUSE | EFUSE programming voltage supply | 1.71 | 1.8 | 1.89 | V |

| DVDD18_EMMC | Power supply for EMMC IO | 1.71 | 1.8 | 1.89 | V |

| DVDD33_EMMC | Power supply for EMMC IO | 3.15 | 3.3 | 3.45 | V |

| TA | Ambient operation temperature | -20 | - | 60 | ℃ |

| TJ | Junction temperature | -40 | - | 125 | ℃ |

| HBM | Human Body Model | - | - | 2000 | V |

| CDM | Charged-Device Model | - | - | 250 | V |

电气特性

| 符号 | 参数 | 最小 | 典型 | 最大 | 单位 | |

|---|---|---|---|---|---|---|

| C910 Freq | Fturbo | Turbo mode | - | 2 | - | GHz |

| F3 | Frequency mode 3 | 1.85 | - | - | GHz | |

| F2 | Frequency mode 2 | 1.5 | - | - | GHz | |

| F1 | Frequency mode 1 | 0.8 | - | - | GHz | |

| F0 | Frequency mode 0 | 0.3 | - | - | GHz | |

| Digital GPIO@1.8V | VIH | Input High Voltage | 0.65*VDDIO | - | VDDIO+0.3 | V |

| VIL | Input Low Voltage | -0.3 | - | 0.35*VDDIO | V | |

| VOH | Output High Voltage | VDDIO-0.45 | - | - | V | |

| VOL | Output Low Voltage | - | - | 0.45 | V | |

| II | Input leakage current (Vin=1.8V or 0V) | -10 | - | 10 | uA | |

| IOZ | Tri-state output leakage current (Vout=1.8V or 0V) | -10 | - | 10 | uA | |

| IOH | High level output current | 0.7 | - | 15.7 | mA | |

| IOL | Low level output current | 0.7 | - | 16.3 | mA | |

| RPU | Pull up resistor | 32 | 48 | 79 | kΩ | |

| RPD | Pull down resistor | 30 | 44 | 68 | kΩ | |

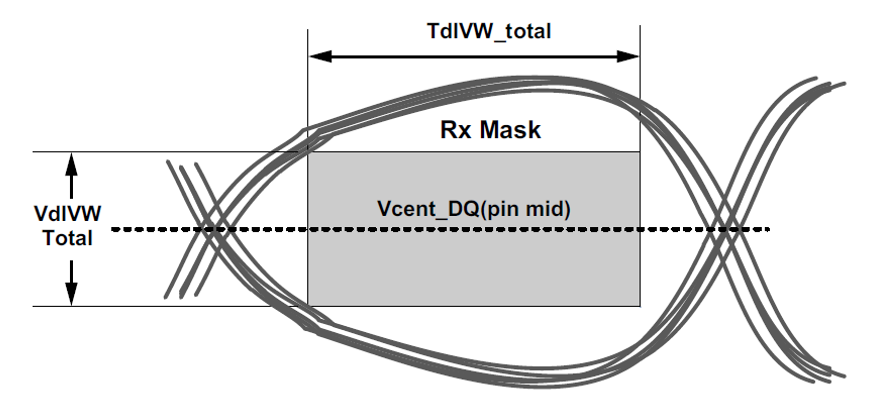

DDR

符合 LPDDR4X 和 LPDDR4 spec。

| 符号 | 参数 | 2133/2400 | 3200 | 4266 | 单位 | |||

|---|---|---|---|---|---|---|---|---|

| 最小 | 最大 | 最小 | 最大 | 最小 | 最大 | |||

| VdlVW_total | Rx Mask voltage-p-p total | - | 140 | - | 140 | - | 120 | mV |

| TdlVW_total | Rx timing window total (At VdlVW voltage levels) | - | 0.22 | - | 0.25 | - | 0.25 | UI |

HDMI 2.0

符合 HDMI2.0 spec。

| 参数 | 最小 | 最大 | 单位 |

|---|---|---|---|

| Single-Ended Low Level Voltage (data channel) | AVcc - 1000 | AVcc - 400 | mV |

| Single-Ended Low Level Voltage (clock channel) | AVcc - 1000 | AVcc - 200 | mV |

| Single-Ended Swing Voltage (data channel) | 400 | 600 | mV |

| Single-Ended Swing Voltage (clock channel) | 200 | 600 | mV |

| Trise/Tfall (data channel) | 42.5 | - | ps |

| Trise/Tfall (clock channel) | 75 | - | ps |

| Inter-pair skew | - | 0.2×Tcharacter | |

| Intra-pair skew | - | 0.15×Tbit | |

| Differential Voltage | -780 | 780 | mV |

| Clock duty cycle | 40 | 60 | % |

| Clock jitter | - | 0.3×Tbit | |

| Data eye diagram eye width (@5.94Gbps) | 67.3 | - | ps |

| Data eye diagram eye height (@5.94Gbps) | 150 | - | mV |

MIPI D-PHY

符合 MIPI D-PHY v1.2 Spec。

| 参数 | 测试基线 | 最小 | 最大 | 单位 |

|---|---|---|---|---|

| HS Data TX 测试 | Static Common Mode Voltage(Vcmtx) | 150 | 250 | mV |

| Common-Level Variations Above 450MHz (Vcmtx (HF)) | - | 15 | mV | |

| Common-Level Variations Between 50-450MHz (Vcmtx (LF)) | - | 25 | mV | |

| Differential Voltage(VOD0 Pulse) | -270 | -140 | mV | |

| Differential Voltage(VOD1 Pulse) | 140 | 270 | mV | |

| Differential Voltage Mismatch (Pulse) | - | 14 | mV | |

| Single Ended Output High Voltage(VOHHS Pulse) | - | 360 | mV | |

| 20%-80% Rise Time (tR)[Burst Data]>1.5Gbps | - | 0.4 | UI | |

| 80%-20% Fall Time (tF)[Burst Data] | - | 0.4 | UI | |

| HS Clock TX 测试 | Static Common Mode Voltage(Vcmtx) | 150 | 250 | mV |

| Vcmtx Mismatch | - | 5 | mV | |

| Common-Level Variations Above 450MHz (Vcmtx (HF)) | - | 15 | mV | |

| Common-Level Variations Between 50-450MHz (Vcmtx (LF)) | - | 25 | mV | |

| Differential Voltage (VOD0 Pulse) | -270 | -140 | mV | |

| Differential Voltage (VOD1 Pulse) | 140 | 270 | mV | |

| Differential Voltage Mismatch (Pulse) | - | 14 | mV | |

| Single Ended Output High Voltage (VOHHS Pulse) | - | 360 | mV | |

| 20%-80% Rise Time (tR)[Burst Clock] | - | 0.4 | UI | |

| 80%-20% Fall Time (tF)[Burst Clock] | - | 0.4 | UI | |

| HS Clock Instantaneous (UIinst)(Max) | - | 12.5 | ns | |

| Clock Lane HS Clock Delta UI (UI variation) | -5% | 5% | UI | |

| Global Operation Data TX 测试 | HS Entry: DATA TLPX | 50 | - | ns |

| HS Entry: DATA TX THS-PREPARE | 40ns + 4×UI | 85ns + 6×UI | ||

| HS Entry: DATA TX THS-PREPARE+THS-ZERO | 145ns + 10×UI | - | ||

| HS Exit: DATA TX THS-TRAIL | 60 ns + 4×UI | - | ||

| HS Exit: DATA TX TREOT | - | 35 | ns | |

| HS Exit: DATA TX TEOT | - | 105 ns + 12×UI | ||

| HS Exit: DATA TX THS-EXIT | 100 | - | ns | |

| Global Operation Clock TX 测试 | HS Entry: CLK TX TLPX | 50 | - | ns |

| HS Entry: CLK TX TCLK-PREPARE | 38 | 95 | ns | |

| HS Entry: CLK TX TCLK-PREPARE+TCLK-ZERO | 300 | - | ns | |

| HS Exit: CLK TX TCLK-POST | 60 ns + 52×UI | - | ns | |

| HS Exit: CLK TX TCLK-TRAIL | 60 | - | ns | |

| HS Exit: CLK TX TREOT | - | 35 | ns | |

| HS Exit: CLK TX TEOT | - | 105ns + 12×UI | ns | |

| HS Exit: CLK TX THS-EXIT | 100 | - | ns | |

| HS Data-Clock timing 测试 | Data-to-Clock Skew (TSKEW(TX))(Max,Min) | -0.2 | 0.2 | UI |

| Data-to-Clock Skew (TSKEW(TX))(Mean) | -0.2 | 0.2 | UI |

USB 3.0

符合 USB3.0 Super Speed GEN1 Spec。

| 参数 | 测试基线 | 最小 | 典型 | 最大 | 单位 |

|---|---|---|---|---|---|

| LFPS test | VTX-DIFF-PP-LFPS | 800 | - | 1200 | mV |

| 5G LFPS Period (tPeriod) | 20 | - | 100 | ns | |

| 5G LFPS Burst Width (tBurst) | 600 | 1000 | 1400 | ns | |

| 5G LFPS Repeat Time Interval (tRepeat) | 6 | 10 | 14 | us | |

| 5G LFPS Rise Time (tRiseFall2080) | - | - | 4 | ns | |

| 5G LFPS Fall Time (tRiseFall2080) | - | - | 4 | ns | |

| 5G LFPS Duty cycle | 40 | - | 60 | % | |

| 5G LFPS AC Common Mode Voltage (VCM-AC-LFPS) | - | - | 100 | mV | |

| SSC test | 5G TSSC-Freq-Dev-Min (tSSC-FREQ-DEVIATION) | -5300 | - | -3700 | ppm |

| 5G TSSC-Freq-Dev-Max | TSSCMin | - | TSSCMax | ppm | |

| 5G SSC Modulation Rate (tSSC-MOD-RATE) | 30 | - | 33 | kHz | |

| 5G SSC Slew Rate (tCDR_SLEW_MAX) | - | - | 10 | ms/s | |

| Eye diagram test | 5G Short Channel Random Jitter | - | - | 46 | ps |

| 5G Short Channel Maximum Deterministic Jitter | - | - | 86 | ps | |

| 5G Short Channel Total Jitter at BER-12 | - | - | 132 | ps | |

| 5G Short Channel Differential Output Voltage | 100 | - | 1200 | mV | |

| 5G Random Jitter (CTLE ON) | - | - | 46 | ps | |

| 5G Far End Maximum Deterministic Jitter (CTLE ON) | - | - | 46 | ps | |

| 5G Far End Total Jitter at BER-12 (CTLE ON) | - | - | 132 | ps | |

| 5G Far End Differential Output Voltage (CTLE ON) | 100 | - | 1200 | mV | |

| RX TEST | jitter tolerance( SJ frequency=0.5MHz) | 2 | - | - | UI |

| jitter tolerance( SJ frequency=1MHz) | 1 | - | - | UI | |

| jitter tolerance( SJ frequency=2MHz) | 0.5 | - | - | UI | |

| jitter tolerance( SJ frequency=4.9MHz) | 0.2 | - | - | UI | |

| jitter tolerance( SJ frequency=10MHz) | 0.2 | - | - | UI | |

| jitter tolerance( SJ frequency=20MHz) | 0.2 | - | - | UI | |

| jitter tolerance( SJ frequency=33MHz) | 0.2 | - | - | UI | |

| jitter tolerance( SJ frequency=50MHz) | 0.2 | - | - | UI |

USB 2.0

符合 USB2.0 Full Speed spec。

| 参数 | 测试基线 | 最小 | 典型 | 最大 | 单位 |

|---|---|---|---|---|---|

| 信号质量测试 | Rise Time | 300 | - | - | ps |

| Fall Time | 300 | - | - | ps | |

| K and J signal amplitudes | Device J Test | -20 | - | 20 | mV |

| Device K Test | -20 | - | 20 | mV | |

| device PACKET 参数测试 | Sync Field Length Test | 63.61 | - | 65.61 | ns |

| EOP Length Test | 15.62 | - | - | ns | |

| Interpacket Gap Between Second and Third Packets | 16.64 | - | 399.4 | ns | |

| Interpacket Gap Between First and Second Packets | 16.64 | - | 399.4 | ns | |

| chirp timing | chirp-K latency | 2.5 | - | 6000 | us |

| chirp-K duration | 1 | - | 7 | ms | |

| suspend/Resume/Reset Timing 测试 | suspend timing response | 3 | - | 3.125 | ms |

| chirp response to reset from Hi-speed operation | 3.1 | - | 6 | ms | |

| chirp response to reset from suspend | 2.5 | - | 6000 | us |

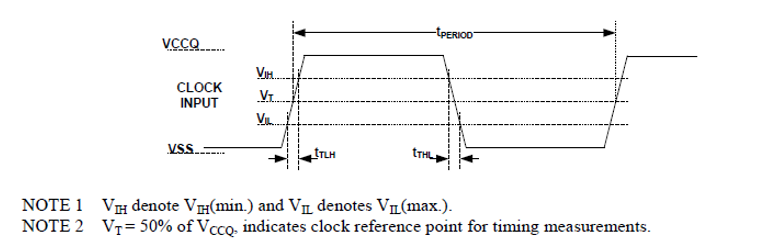

eMMC

符合 JESD84-B51 spec。

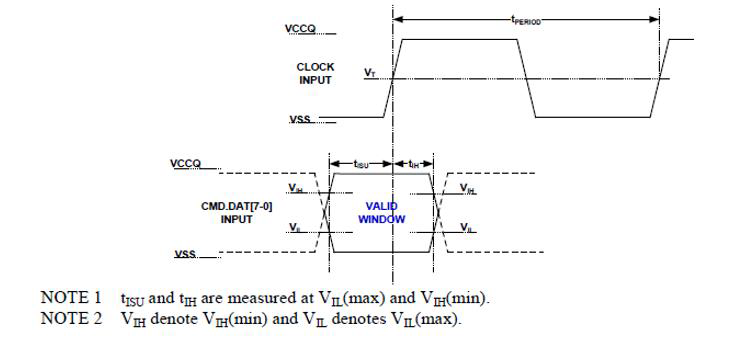

- HS200 时钟时序

| 符号 | 最小 | 最大 | 单位 | 备注 |

|---|---|---|---|---|

| tPERIOD | 5 | - | ns | 200 MHz(max),between rising edges |

| tTLH,tTHL | - | 0.2×tPERIOD | ns | tTLH,tTHL<1ns(max) at 200MHz, CDEVICE=6pF, the absolute maximum value of tTLH,tTHL is 10ns regardless of clock frequency |

| Duty Cycle | 30 | 70 | % |

- HS200 输入信号时序

| 符号 | 最小 | 最大 | 单位 | 备注 |

|---|---|---|---|---|

| tISU | 1.40 | - | ns | CDEVICE≤6pF |

| tIH | 0.8 | - | ns | CDEVICE≤6pF |

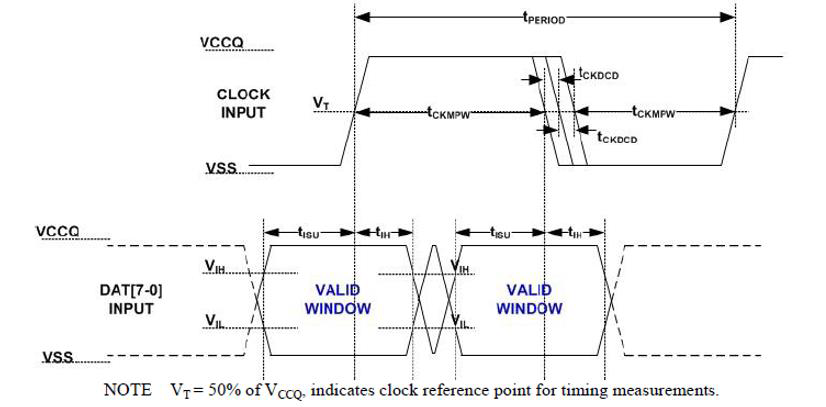

- HS400 时钟/输入信号时序

| 参数 | 符号 | 最小 | 最大 | 单位 | 备注 |

|---|---|---|---|---|---|

| Input CLK | |||||

| Cycle time data transfer mode | tPERIOD | 5 | - | ns | 200MHz(max),between rising edges with respect to Vt |

| Slew rate | SR | 1.125 | - | V/ns | With respect to VIH/VIL |

| Duty cycle distortion | tCKDCD | 0.0 | 0.3 | ns | Allowable deviation from an ideal 50% duty cycle With respect to Vt Includes jitter, phase noise |

| Minimum pulse width | tCKMPW | 2.2 | - | ns | With respect to Vt |

| Input DAT(referenced to CLK) | |||||

| Input set-up time | tISUddr | 0.4 | - | ns | CDEVICE≤6pF With respect to VIH/VIL |

| Input hold time | tIHddr | 0.4 | - | ns | CDEVICE≤6pF With respect to VIH/VIL |

| Slew rate | SR | 1.125 | - | V/ns | With respect to VIH/VIL |

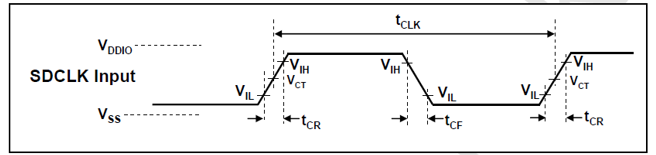

SD

符合 Physical Layer Specification version3.00 Spec。

- 时钟信号时序

| 符号 | 最小 | 最大 | 单位 | 备注 |

|---|---|---|---|---|

| tCLK | 4.80 | - | ns | 208MHz(max), between rising edges, VCT=0.975V |

| tCR, tCF | - | 0.2×tCLK | ns | tCR,tCF<0.96ns(max) at 208MHz, CCARD=10pF, tCR,tCF<2.00ns(max) at 100MHz, CCARD=10pF |

| Duty Cycle | 30 | 70 | % |

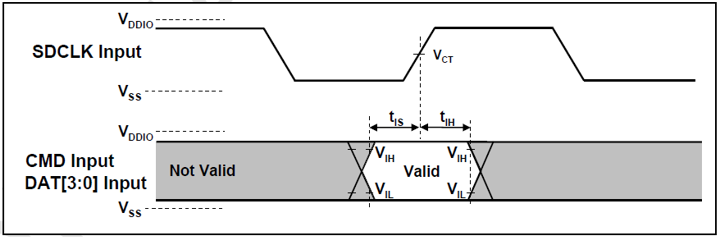

- SDR50/SDR104 输入信号时序

| 参数 | 符号 | 最小 | 最大 | 单位 | 备注 |

|---|---|---|---|---|---|

| SDR104 mode | tIS | 1.40 | - | ns | CCARD=10pF,VCT=0.975V |

| tIH | 0.8 | - | ns | CCARD=5pF,VCT=0.975V | |

| SDR50 mode | tIS | 3.00 | - | ns | CCARD=10pF,VCT=0.975V |

| tIH | 0.8 | - | ns | CCARD=5pF,VCT=0.975V |

GMAC

| 参数 | 测试基线 | 最小 | 典型 | 最大 | 单位 |

|---|---|---|---|---|---|

| Tcyc | Clock Cycle Duration | 7.2 | 8 | 8.8 | ns |

| Duty_G | Duty Cycle for Gigabit | 45 | 50 | 55 | % |

| trCLK | Clock Fall Time(20%-80%) | - | - | 0.75 | ns |

| tfCLK | Clock Fall Time(20%-80%) | - | - | 0.75 | ns |

| Tskew_DATA | Data0 to Clock output Skew | -0.5 | - | 0.5 | ns |

| tVaild_window_high_DATA | Data0 high vaild window | 2 | - | - | ns |

| tVaild_window_low_DATA | Data0 low vaild window | 2 | - | - | ns |

I2C

符合 I2C Spec。

| 参数 | 测试基线 | ��最小 | 典型 | 最大 | 单位 |

|---|---|---|---|---|---|

| 100kbps | SCL 时钟频率 fSCL | 0 | - | 100 | kHz |

| SCL 上升时间 tr | - | - | 1000 | ns | |

| SCL 下降时间 tf | - | - | 300 | ns | |

| SDA 上升时间 tr | - | - | 1000 | ns | |

| SDA 下降时间 tf | - | - | 300 | ns | |

| SCL 低电平脉宽 tLOW | 4.7 | - | - | us | |

| SCL 高电平脉宽 tHIGH | 4 | - | - | us | |

| 数据信号建立时间 tSU;DAT | 250 | - | - | ns | |

| 数据信号保持时间 tHD;DAT | 0 | - | - | ns | |

| 启动信号保持时间th;STA | 4 | - | - | us | |

| 结束信号建立时间 tSU;STO | 4 | - | - | us | |

| 400kbps | SCL 时钟频率 fSCL | 0 | - | 400 | kHz |

| SCL 上升时间 tr | 20 | - | 300 | ns | |

| SCL 下降时间 tf | 6.5 | - | 300 | ns | |

| SDA 上升时间 tr | 20 | - | 300 | ns | |

| SDA 下降时间 tf | 6.5 | - | 300 | ns | |

| SCL 低电平脉宽 tLOW | 1.3 | - | - | us | |

| SCL 高电平脉宽 tHIGH | 0.6 | - | - | us | |

| 数据信号建立时间 tSU;DAT | 100 | - | - | ns | |

| 数据信号保持时间 tHD;DAT | 0 | - | - | ns | |

| 启动信号保持时间 th;STA | 0.6 | - | - | us | |

| 结束信号建立时间 tSU;STO | 0.6 | - | - | us | |

| 1.7Mbps | SCL 时钟频率 fSCL | 0 | - | 1700 | kHz |

| SCL 上升时间 tr | 20 | - | 80 | ns | |

| SCL 下降时间 tf | 20 | - | 80 | ns | |

| SDA 上升时间 tr | 20 | - | 160 | ns | |

| SDA 下降时间 tf | 20 | - | 160 | ns | |

| SCL 低电平脉宽 tLOW | 0.32 | - | - | us | |

| SCL 高电平脉宽 tHIGH | 0.12 | - | - | us | |

| 数据信号建立时间 tSU;DAT | 10 | - | - | ns | |

| 数据信号保持时间 tHD;DAT | 0 | - | 150 | ns | |

| 启动信号保持时间 th;STA | 0.16 | - | - | us | |

| 结束信号建立时间 tSU;STO | 0.16 | - | - | us |

PLL/RC/CLOCK

| 符号分类 | 符号 | 参数 | 最小 | 典型 | 最大 | 单位 |

|---|---|---|---|---|---|---|

| PLL | Fout | Output frequency range | 16 | - | 3200 | MHz |

| Tlock | Lock time | - | 256 | 512 | cycle | |

| Power consumption (FVCO = 3200MHz) | - | 12.6 | 15.12 | mW | ||

| Period jitter (random, VCO = 3200MHz) | - | - | 0.26 | ps | ||

| Junction temperature | -40 | 25 | 125 | ℃ | ||

| RC | Intrinsic Oscillator Frequency | - | 24 | - | MHz | |

| Duty Cycle on FOUT | 47 | - | 53 | % | ||

| Total frequency Variation | -3 | - | 3 | % | ||

| Initial Settling Time | - | 140 | 220 | us | ||

| Period Jitter (RMS) | - | - | 0.45 | ns | ||

| Clock | FOSC | Input clock frequency | - | 24 | - | MHz |

| FRTC | Input clock frequency | - | 32.768 | - | kHz | |

| DCRTC | Duty cycle | 45 | 50 | 55 | % |

TDM/PDM/I2S/SPDIF/7816

| 符号 | 参数 | 最小 | 典型 | 最大 | 单位 | |

|---|---|---|---|---|---|---|

| I2S | fMCK | I2S main clock output | - | 256fs or 384fs | - | kHz |

| tHC/tLC | clock HIGH/LOW | 0.35T | - | - | ns | |

| thtr | hold time | 0 | - | - | ns | |

| tdtr | delay | - | - | 0.8T | ns | |

| TDM | F(BCLK) | BCLK Frequency | - | fs×bits×channels | - | kHz |

| tr(BCLK) | BCLK rise time | - | - | 20 | ns | |

| tf(BCLK) | BCLK fall time | - | - | 20 | ns | |

| td(D-B) | BCLK to SDOUT delay | - | - | 20 | ns | |

| PDM | f(PDMCLK) | PDMCLK clock frequency | - | 0.768 or 1.536 | - | MHz |

| tSETUP | PDM_DATA to PDM_CLK Setup Time | 10 | - | - | ns | |

| tHOLD | PDM_DATA to PDM_CLK Hold Time | 10 | - | - | ns | |

| SPDIF | f(CLK) | Bit rate | - | 64×FS | - | Mbit/s |

| ISO7816 | CLK | frequency | - | 1.0417 | 15.625 | MHz |

| Ta | IO set to state H time | - | - | 200/f | ||

| Tb | RST at state L time | 400/f | - | - | ||

| Tc | answer on IO after RST rise | 400/f | - | 40000/f | ||

T SENSOR/eFUSE Electrical Characteristics

| 符号 | 参数 | 最小 | 典型 | 最大 | 单位 | |

|---|---|---|---|---|---|---|

| Tsensor | Range | -40 | - | 125 | ℃ | |

| Eun-cal | Un-cal error from -40~125℃ | -3 | - | 3 | ℃ | |

| Eone-cal | error with one-point-calibration 100℃ cal (range 80~120℃) | -1 | - | 1 | ℃ | |

| Etwo-cal | error with 20/100℃ two-point-calibration (range 20~100℃) | -1.25 | - | 1.25 | ℃ | |

| eFUSE | Ipgm_vdd | VDD current in PGM mode | 2 | 4 | 190 | uA |

| Ipgm_vqps | VQPS current in PGM mode | - | 61.349 | 98.280 | mA | |

| Istandby_vdd | VDD current in standby mode | 0.242 | 0.398 | 21.785 | uA | |